#### **MODULE 4**

Interfacing Memory, I/O, 8255 - Detailed study - Architecture, Control word format and modes of operation, Architecture and modes of operation of 8279 and 8257 (Just mention the control word, no need to memorize the control word format)

# **MODULE 4**

#### Semiconductor Memory Interfacing:

Semiconductor memories are of two types, viz. RAM (Random Access Memory) and ROM (Read Only Memory).

# Static RAM Interfacing: Q. Explain the general procedure of static memory interfacing with 8086?

The semiconductor RAMs are of broadly two types-static RAM and dynamic RAM. The semiconductor memories are organized as two dimensional arrays of memory locations. For example, 4K x 8 or 4K byte memory contains 4096 locations, where each location contains 8bit data and only one of the 4096 locations can be selected at a time. Obviously, for addressing 4K bytes of memory, twelve address lines are required. In general, to address a memory location out of N memory locations, we will require at least *n* bits of address, i.e. *n* address lines where n = Log2 N. Thus if the microprocessor has *n* address lines, then it is able to address at the most N locations of memory, where  $2^n = N$ . However, if out of *N* locations only *P* memory locations are to be interfaced, then the least significant *p* address lines out of the available *n* lines can be directly connected from the microprocessor to the memory chip while the remaining (n-p) higher order address lines may be used for address decoding (as inputs to the chip selection logic). The memory address depends upon the hardware circuit used for decoding the chip select (CS). The output of the decoding circuit is connected with the CS pin of the memory chip.

The general procedure of static memory interfacing with 8086 is briefly described as follows:

1. Arrange the available memory chips so as to obtain 16-bit data bus width. The upper 8-bit bank is called 'odd address memory bank' and the lower 8-bit bank is called 'even address memory bank'.

2. Connect available memory address lines of memory chips with those of the microprocessor and also connect the memory RD and WR inputs to the corresponding processor control signals. Connect the 16-bit data bus of the memory bank with that of the microprocessor 8086.

3. The remaining address lines of the microprocessor, BHE and A0 are used for decoding the required chip select signals for the odd and even memory banks. CS of memory is derived from the O/P of the decoding circuit .

As a good and efficient interfacing practice, the address map of the system should be continuous as far as possible, i.e. there should be no windows in the map. A memory location should have a single address corresponding to it, i.e. absolute decoding should be preferred, and minimum hardware should be used for decoding. In a number of cases, linear decoding may be used to minimise the required hardware. Let us now consider a few example problems on memory interfacing with 8086.

#### Problem 5.1

Interface two 4K  $\times$  8 EPROMS and two 4K  $\times$  8 RAM chips with 8086. Select suitable maps.

**Solution** We know that, after reset, the IP and CS are initialised to form address FFFF0H. Hence, this address must lie in the EPROM. The address of RAM may be selected any where in the 1MB address space of 8086, but we will select the RAM address such that the address map of the system is continuous, as shown in Table 5.1.

| Address | A19 | A <sub>18</sub> | A <sub>17</sub> | A <sub>16</sub> | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> | A <sub>09</sub> | A <sub>08</sub> | A <sub>07</sub> | A <sub>06</sub> | A <sub>05</sub> _ | A <sub>04</sub> | A <sub>03</sub> | A <sub>02</sub> | A <sub>01</sub> | :A <sub>00</sub> |

|---------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|

| FFFFFH  | 1   | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1                 | 1               | 1               | 1               | 1               | 1                |

|         |     |                 |                 |                 |                 | EPR             | OM              |                 |                 |                 |                 |                 | 3K×             | 8               |                   |                 |                 |                 |                 | 183              |

| FE000H  | 1   | 1               | 1               | 1               | 1               | 1               | 1               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0                 | 0               | 0               | 0               | 0               | 0                |

| FDFFFH  | 1   | 1               | 1               | 1               | 1               | 1               | 0               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1                 | 1               | 1               | 1               | 1               | 1                |

|         |     |                 |                 |                 |                 | R               | AM              | *               |                 |                 | 8               | $K \times$      | 8               | 5               |                   |                 |                 |                 |                 |                  |

| FC000H  | 1   | 1               | 1               | 1               | 1               | 1               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0                 | 0               | 0               | 0               | 0               | 0                |

Table 5.1 Memory Map for Problem 5.1

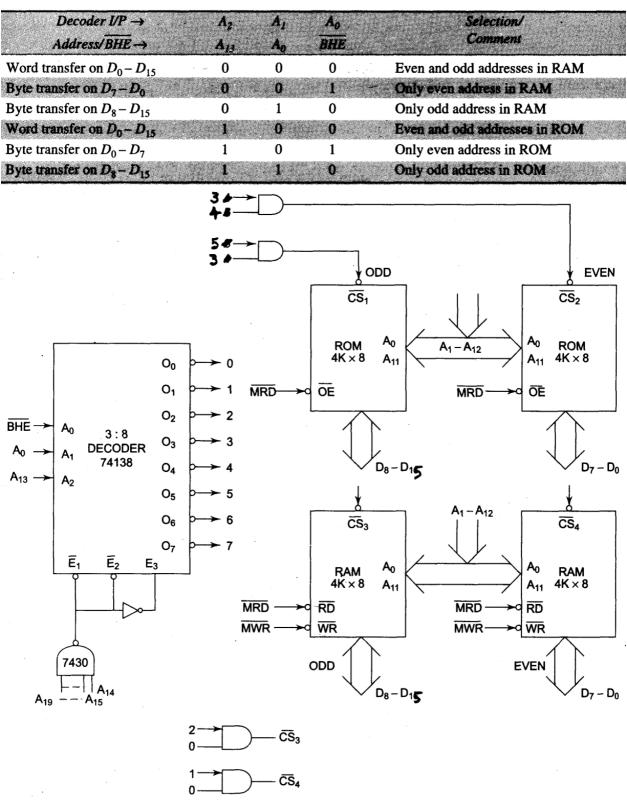

Total 8K bytes of EPROM need 13 address lines  $A_0 - A_{12}$  (since  $2^{13} = 8K$ ). Address lines  $A_{13} - A_{19}$  are used for decoding to generate the chip select. The  $\overline{BHE}$  signal goes low when a transfer is at odd address or higher byte of data is to be accessed. Let us assume that the latched address,  $\overline{BHE}$  and demultiplexed data lines are readily available for interfacing. Figure 5.1 shows the interfacing diagram for the memory system.

The memory system in this example contains in total four  $4K \times 8$  memory chips.

The two 4K × 8 chips of RAM and ROM are arranged in parallel to obtain 16-bit data bus width. If  $A_0$  is 0, i.e. the address is even and is in RAM, then the lower RAM chip is selected indicating 8-bit transfer at an even address. If  $A_0$  is 1, i.e. the address is odd and is in RAM, the BHE goes low, the upper RAM chip is selected, further indicating that the 8-bit transfer is at an odd address. If the selected addresses are in ROM, the respective ROM chips are selected. If at a time  $A_0$  and BHE both are 0, both the RAM or ROM chips are selected, i.e. the data transfer is of 16 bits. The selection of chips here takes place as shown in Table 5.2.

Table 5.2

Memory Chip Selection for Problem 5.1

Fig. 5.1 Interfacing Problem 5.1

#### Problem 5.2

Design an interface between 8086 CPU and two chips of 16K × 8 EPROM and two chips of 32K × 8 RAM. Select the starting address of EPROM suitably. The RAM address must start at 00000H.

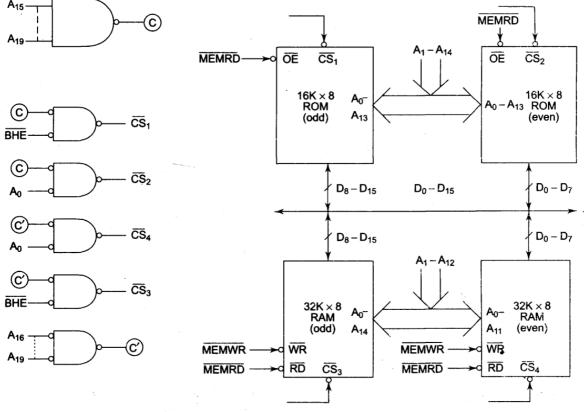

Solution: The last address in the map of 8086 is FFFFFH. After resetting, the processor starts from FFFF0H. Hence this address must lie in the address range of EPROM. Figure 5.2 shows the interfacing diagram, and Table 5.3 shows complete map of the system.

|           |       |     |       | Т     | able | 5.3  | Add  | iress i         | Мар             | for P           | roble           | m 5.2           | 2               |     |                 |                 |                 |                 |                 |

|-----------|-------|-----|-------|-------|------|------|------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|

| Addresses | A19 . | A18 | 417 A | 16 A1 | 5 A1 | A 13 | A12  | A <sub>II</sub> | A <sub>10</sub> | A <sub>09</sub> | A <sub>08</sub> | A <sub>07</sub> | A <sub>06</sub> | Aos | A <sub>04</sub> | A <sub>03</sub> | A <sub>02</sub> | A <sub>01</sub> | A <sub>00</sub> |

| FFFFFH    | 1     | 1   | 1 1   | 1     | 1    | 1    | 1    | 1               | 1               | 1               | 1               | 1               | 1               | 1   | 1               | 1               | 1               | 1               | 1               |

|           |       |     |       | 222   |      |      | 32KF | 3               | E               | PRO             | M               |                 |                 |     | Series.         |                 |                 |                 |                 |

| F8000H    | 1     | 1   | 1 1   | 1     | 0    | 0    | 0    | 0               | 0               | 0               | 0               | 0               | 0               | 0   | 0               | 0               | 0               | 0               | 0               |

| OFFFFH    | 0     | 0   | 0 0   | 1 1   | 1    | 1    | 1    | 1               | 1               | 1               | 1               | 1               | 1               | 1   | 1               | 1               | 1               | 1               | 1               |

|           | -     |     |       | I     | 6    | 4KB  | RAM  | [               |                 |                 |                 |                 |                 |     |                 |                 |                 |                 |                 |

| 00000H    | 0     | 0   | 0 0   | )   0 | 0    | 0    | 0    | 0               | 0               | 0               | 0               | 0               | 0               | 0   | 0               | 0               | 0               | 0               | 0               |

It is better not to use a decoder to implement the above map because it is not continuous, i.e. there is some unused address space between the last RAM address (OFFFFH) and the first EPROM address F8000H). Hence the logic is implemented using logic gates, as shown in Fig. 5.2.

Interfacing Problem 5.2 Fig. 5.2

#### Problem 5.3

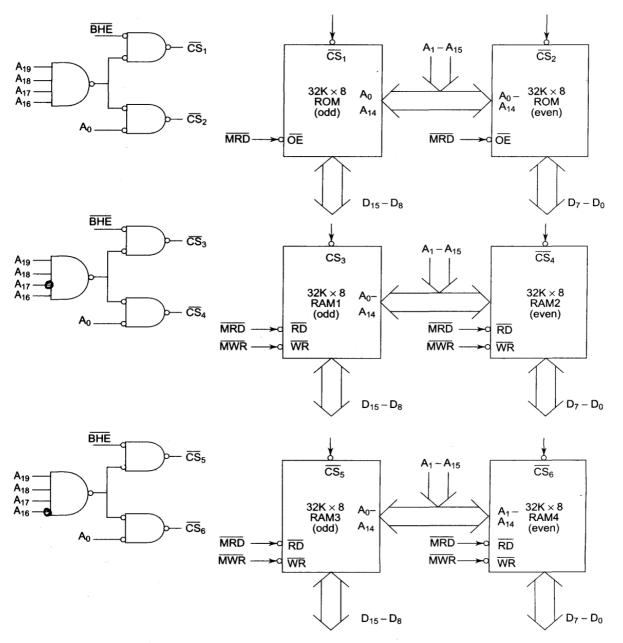

It is required to interface two chips of 32K  $\times$  8 ROM and four chips of 32K  $\times$  8 RAM with 8086, according to the following map.

ROM 1 and 2 F0000H - FFFFFH, RAM 1 and 2 D0000H - DFFFFH RAM 3 and 4 E0000H - EFFFFH

Show the implementation of this memory system.

Solution Let us write the memory map of the system as shown in Table 5.6.

The implementation of the above map is shown in Fig. 5.3 using the same technique as in Problem 5.1 and Problem 5.2. All the address, data and control signals are assumed to be readily available.

Fig. 5.3 Interfacing Problem 5.3

Q.A circuit containing 32KB of RAMis to be interfaced to an 8086 based system, so that the first address of the RAM is at 48000H .What is the entire range of the RAM address ?What address lines should be used?

ANS:

32 KB=2<sup>5</sup>x2<sup>10</sup>=2<sup>15</sup>

| 4                                                  | $8 \longrightarrow F$                                               | $0 \longrightarrow F$                                     | $0 \longrightarrow F$                                     | $0 \longrightarrow F$                                |

|----------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|

| $\substack{A_{19}\\A_{18}\\A_{17}\\A_{17}\\A_{16}$ | $\begin{array}{c}A_{15}\\A_{14}\\A_{13}\\A_{12}\\A_{12}\end{array}$ | $\begin{array}{c}A_{11}\\A_{10}\\A_{9}\\A_{8}\end{array}$ | $\begin{array}{c} A_7\\ A_6\\ A_5\\ A_5\\ A_4\end{array}$ | $\begin{array}{c} A_{3}\\ A_{1}\\ A_{0} \end{array}$ |

| 0 1 0 0                                            | 1 X X X                                                             | XXXX                                                      | ХХХХ                                                      | ХХХХ                                                 |

| Ĩ                                                  |                                                                     |                                                           | Ĩ                                                         |                                                      |

|                                                    | K—Don't care                                                        | (Use 0 or 1)                                              |                                                           |                                                      |

So range of address could be

| A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 0   | 1   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

|     | RAM |     |     |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

| 0   | 1   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

le 48000H to 4FFFFH

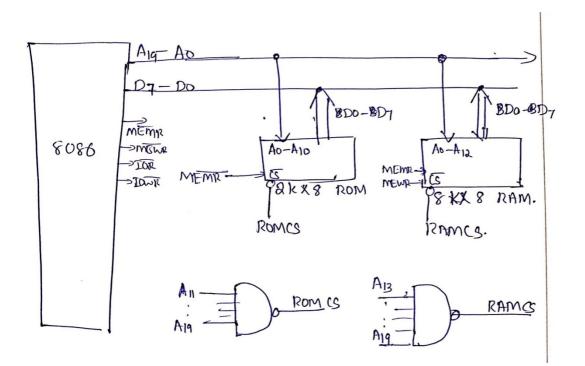

Q.Give an interfacing circuit to interface a 2K bytes of EPROM and four 2K bytes of RAM to 8086.Starting address of EPROM is 00000H and that of RAM is 60000H.Give memory map of your system and Explain the chip select logic?

ANS:

ROM= 2KB (Addr lines needed=11)

RAM=four 2KB RAM's=8KB RAM (Addr lines needed=13)

**Address Map**

| Addre | A1  | A1  | А | Α | А | А | А | А | А | А | Α | А |

|-------|----|----|----|----|----|----|----|----|-----|-----|---|---|---|---|---|---|---|---|---|---|

| SS    | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0   | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 007F  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| F     |    |    |    |    |    |    |    |    |     |     |   |   |   |   |   |   |   |   |   |   |

|       |    |    |    |    |    |    |    |    | R   | ROM |   |   |   |   |   |   |   |   |   |   |

| 0000  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0     |    |    |    |    |    |    |    |    |     |     |   |   |   |   |   |   |   |   |   |   |

| 61FF  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 1   | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| F     |    |    |    |    |    |    |    |    |     |     |   |   |   |   |   |   |   |   |   |   |

|       |    |    |    |    |    |    |    | ]  | RAM |     |   |   |   |   |   |   |   |   |   |   |

| 6000  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0 | 0 | 0 | 0 | 0 |   | 0 | 0 | 0 | 0 |

| 0     |    |    |    |    |    |    |    |    |     |     |   |   |   |   |   |   |   |   |   |   |

# Q.Design memory interfacing circuit for interfacing 4Kx8 RAM and 2Kx8 Rom using 3 to 8 decorder?(Kerala university)

ANS: Split 4Kx8 RAM into two 2Kx8 Chips and

# **Dynamic RAM Interfacing**

Q.Write the advantages of dynamic RAM interfacing?

Q.What do you mean by refresh cycle in dynamic RAM ?

Q.Explain the use of dynamic RAM controller in interfacing DRAM with 8086?

Whenever a large capacity memory is required in a microcomputer system, the memory subsystem is generally designed using dynamic RAM because there are various advantages of dynamic RAM.

• E.g. higher packing density, lower cost and less power consumption. A typical static RAM cell may require six transistors while the dynamic RAM cell requires only a transistors along with a capacitor. Hence it is possible to obtain higher packaging density and hence low cost units are available.

• The basic dynamic RAM cell uses a capacitor to store the charge as a representation of data. This capacitor is manufactured as a diode that is reverse biased so that the storage capacitance comes into the picture.

• This storage capacitance is utilized for storing the charge representation of data but the reverse-biased diode has leakage current that tends to discharge the capacitor giving rise to the possibility of data loss. To avoid this possible data loss, the data stored in a dynamic RAM cell must be refreshed after a fixed time interval regularly. The process of refreshing the data in RAM is called as **Refresh cycle.**

• The refresh activity is similar to reading the data from each and every cell of memory, independent of the requirement of microprocessor. During this refresh period all other operations related to the memory subsystem are suspended. Hence the refresh activity causes loss of time, resulting in reduces system performance.

# • However keeping in view the advantages of dynamic RAM, like low power consumption, high packaging density and low cost, most of the advanced computing system are designed using dynamic RAM, at the cost of operating speed.

• A dedicated hardware chip called as **dynamic RAM controller** is the most important part of the interfacing circuit.

The Refresh cycle is different from the memory read cycle in the following aspects.

1. The memory address is not provided by the CPU address bus, rather it is generated by a refresh mechanism counter called as **refresh counter**.

2. Unlike memory read cycle, more **than one memory chip** may be enabled at a time so as to **reduce the number of total memory refresh cycles.**

3. The data enable control of the selected memory chip is deactivated, and data is not allowed to appear on the system data bus during refresh, as more than one memory units are refreshed simultaneously. This is to avoid the data from the different chips to appear on the bus simultaneously.

4. Memory **read is either a processor initiated** or **an external bus master initiated** and carried out by the refresh mechanism.

• Dynamic RAM is available in units of several kilobits to megabits of memory. This memory is arranged internally in a two dimensional matrix array so that it will have n rows and m columns. The row address n and column address m are important for the refreshing operation.

• For example, a typical 4K bit dynamic RAM chip has an internally arranged bit array of dimension 64 \* 64, i.e. 64 rows and 64 columns. The row address and column address will require 6 bits each. These 6 bits for each row address and column address will be generated by the refresh counter, during the refresh cycles.

• A complete row of 64 cells is refreshed at a time to minimizes the refreshing time. Thus the refresh counter needs to generate only row addresses. The row address are multiplexed, over lower order address lines.

• The **refresh signals act to control the multiplexer**, i.e. when refresh cycle is in process the refresh counter puts the row address over the address bus for refreshing. Otherwise, the address bus of the processor is connected to the address bus of DRAM, during normal processor initiated activities.

• A timer, **called refresh timer**, derives a pulse for refreshing action after each refresh interval.

• Refresh interval can be qualitatively defined as the time for which a dynamic RAM cell can hold data charge level practically constant, i.e. no data loss takes place.

• Suppose the typical dynamic RAM chip has 64 rows, then each row should be refreshed after each refresh interval or in other words, all the 64 rows are to refreshed in a single refresh interval.

• This refresh interval depends upon the manufacturing technology of the dynamic RAM cell. It may range anywhere from **1ms to 3ms.**

• Let us consider **2ms as a typical refresh time interval**. Hence, the frequency of the refresh pulses will be calculated as follows:

• Refresh Time (per row) tr =  $(2 * 10^{-3}) / 64$ .

(ie Refresh time per row = Refresh time /No.of rows)

• Refresh Frequency  $fr = 64 / (2 * 10^{-3}) = 32 * 10^{3} Hz.$

#### **Problem**

A 4k bit dynamic RAM with 2 ms of refresh time interval. find the refresh frequency of the RAM?

Solution:

A typical 4K bit dynamic RAM chip has an internally arranged bit array of dimension 64 \* 64 , i.e. 64 rows and 64 columns.

• Refresh Time (per row) tr = (2 \* 10<sup>-3</sup>) / 64.

(ie Refresh time per row = Refresh time /No.of rows)

• Refresh Frequency  $fr = 64 / (2 * 10^{-3}) = 32 * 10^{3}$  Hz.

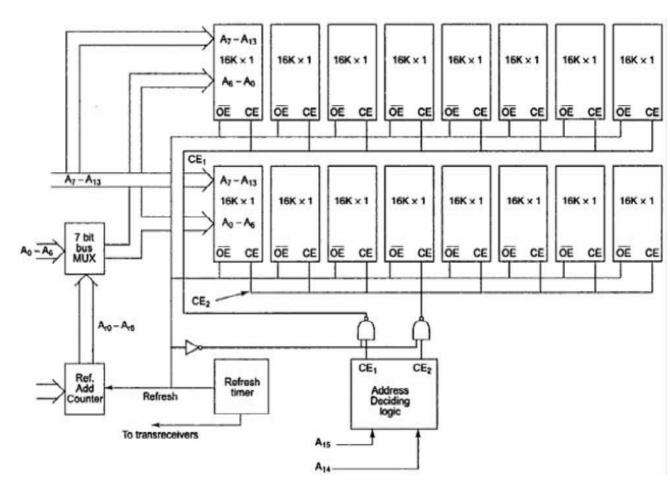

• The following block diagram explains the refreshing logic and 8086 interfacing with dynamic RAM.

• Each chip is of 16K \* 1-bit dynamic RAM cell array. The system contains two 16K byte dynamic RAM units. All the address and data lines are assumed to be available from an 8086 microprocessor system

The OE pin controls output data buffer of the memory chips. The CE pins are active high chip selects of memory chips. The refresh cycle starts, if the refresh output of the refresh timer goes high, OE and CE also tend to go high.

• The high CE enables the memory chip for refreshing, while high OE prevents the data from appearing on the data bus, as discussed in memory refresh cycle. The 16K \* 1-bit dynamic RAM has an internal array of 128\*128 cells, requiring 7 bits for row address. The lower order seven lines A0-A6 are multiplexed with the refresh counter output A10-A16.

FIG:ynamic RAM Refreshing Logic

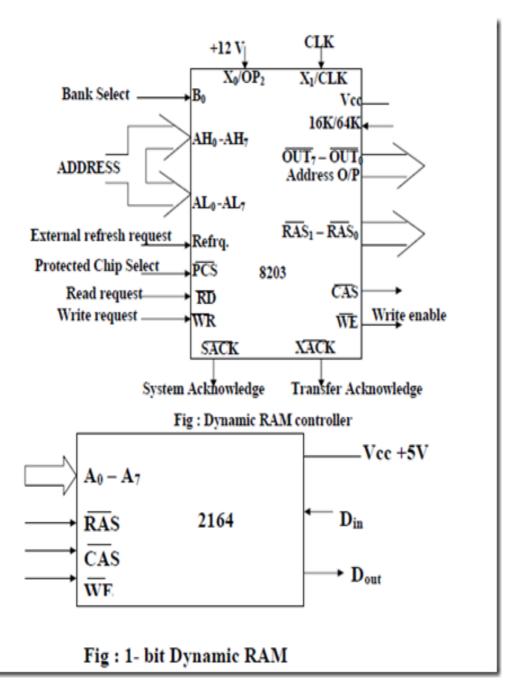

The pin assignment for 2164 dynamic RAM is as in above fig.

• The RAS and CAS are row and column address strobes and are driven by the dynamic RAM controller outputs. A0 -A7 lines are the row or column address lines, driven by the OUT0 - OUT7 outputs of the controller. The WE pin indicates memory write cycles. The DIN and DOUT pins are data pins for write and read operations respectively.

• In practical circuits, the refreshing logic is integrated inside dynamic RAM controller chips like 8203, 8202, 8207 etc.

Intel's 8203 is a dynamic RAM controller that support 16K or 64K dynamic RAM chip. This selection is done using pin 16K/64K. If it is high, the 8203 is configured to control 16K dynamic RAM, else it controls 64K dynamic RAM. The address inputs of 8203 controller accepts address lines A1 to A16 on lines AL0-AL7 and AH0-AH7.

• The A0 lines is used to select the even or odd bank. The RD and WR signals decode whether the cycle is a memory read or memory write cycle and are accepted as inputs to 8203 from the microprocessor.

• The WE signal specifies the memory write cycle and is not output from 8203 that drives the WE input of dynamic RAM memory chip. The OUT0 – OUT7 set of eight pins is an 8-bit output bus that carries multiplexed row and column addresses are derived from the address lines A1-A16 accepted by the controller on its inputs AL0-AL7 and AH0-AH7.

• An external crystal may be applied between X0 and X1 pins, otherwise with the OP2 pin at +12V, a clock signal may be applied at pin CLK.

• The PCS pin accepts the chip select signal derived by an address decoder. The REFREQ pin is used whenever the memory refresh cycle is to be initiated by an external signal.

• The XACK signal indicates that data is available during a read cycle or it has been written if it is a write cycle. It can be used as a strobe for data latches or as a ready signal to the processor.

• The SACK output signal marks the beginning of a memory access cycle.

• If a memory request is made during a memory refresh cycle, the SACK signal is delayed till the starring of memory read or write cycle. • Above fig shows the 8203 can be used to control a 256K bytes memory subsystem for a maximum mode 8086 microprocessor system.

• This design assumes that data and address busses are inverted and latched, hence the inverting buffers and inverting latches are used (8283-inverting buffer and 8287- inverting latch).

# **Interfacing I/O Ports**

# Q.Describe the Steps in Interfacing an I/O Devices?

I/O ports or input/output ports are the devices through which the microprocessor communicates with other devices or external data sources/destinations. Input activity, as one may expect, is the activity that enables the microprocessor to read data from external devices, for example keyboard, joysticks, mouser etc. the devices are known as input devices as they feed data into a microprocessor system.

Output activity transfers data from the microprocessor top the external devices, for example CRT display, 7 segment displays, printer, etc, the devices that accept the data from a microprocessor system are called output devices.

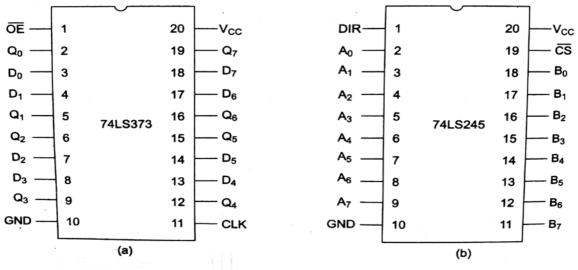

The figure beloe shows two chips,74LS373 and 74LS245.

74LS373 contains 8 buffered latches and can be used as **an 8-bit output port**. And 74LS245. Contains 8 buffers that may be used as **an 8 –bit input port**.

Fig. 5.11 (a) Latch (O/P Port) (b) Buffer (I/P Port)

**DIR pin:-** selects direction of data transfer of 74LS245(input port) if DIR=1,direction is from A(i/p)-B(o/p) and otherwise from B(i/p)-A(o/p)

$\overline{OE}$  and  $\overline{CS}$  :-chip selects of 74LS373 and 74LS245

D's and Q's are corresponding latch inputs and outputs respectively

#### Steps in Interfacing an I/O Device

The following steps are performed to interface a general I/O device with a CPU:

1. Connect the data bus of the microprocessor system with the data bus of the I/O port.

2. Derive a device address pulse by decoding the required address of the device and use it as the chip select of the device.

3. Use a suitable control signal, i.e. IORD and /or IOWR to carry out device operations, i.e. connect IORD to RD input of the device if it is an input devise, otherwise connect IOWR to WR input of the device. In some cases the RD or WR control signals are combined with the device address pulse to generate the device select pulse.

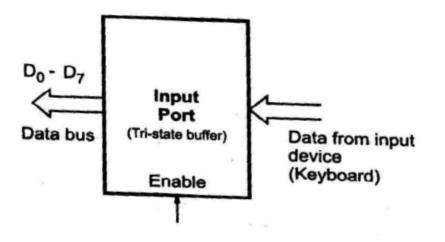

#### **Input Port**

The input device is connected to the microprocessor through buffer. The simplest form of a input port is a buffer as shown in the figure.

This buffer is a tri-state buffer and its output is available only when enable signal is active. When microprocessor wants to read data from the input device (keyboard), the control signals from the microprocessor activates the buffer by asserting enable input of the buffer. Once the buffer is enabled, data from the device is available on the data bus. Microprocessor reads this data by initiating read command.

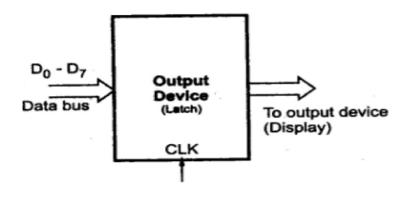

#### **Output Port**

It is used to send the data to the output device such as display from the microprocessor. The simplest form of the output port is a latch.

The output device is connected to the microprocessor through latch as shown in the figure. When microprocessor wants to send data to the output device it puts the data on the data bus and activates the clock signal of the latch, latching the data from the data bus at the output of latch. It is then available at the output of latch for the output device

#### I/O Interfacing Techniques

# Q.Describe the two different methods of interfacing I/O devices?

# Q.Differentiate memory mapped I/O and I/O mapped I/O?

Input/output devices can be interfaced with microprocessor systems in two ways :

# 1. I/O mapped I/O

# 2. Memory mapped I/O

# 1. I/O mapped I/O :

I/O devices have a **separate address space from general memory**, either accomplished by an extra "I/O" pin on the CPU's physical interface, or an entire bus dedicated to I/O. Because the address space for I/O is isolated from that for main memory, this is sometimes referred to as isolated I/O.

8086 has special instructions IN and OUT to transfer data through the input/output ports in I/O mapped I/O system. The IN instruction copies data from a port to the Accumulator. If an 8-bit port is read data will go to AL and if 16-bit port is read the data will go to AX. The OUT instruction copies a byte from AL or a word from AX to the specified port. The M/IO signal is always low when 8086 is executing these instructions. In this address of I/O device is 8-bit or 16-bit. It is 8-bit for Direct addressing and 16-bit for Indirect addressing.

# 2. Memory mapped I/O

Memory-mapped I/O uses the **same address space** to address both memory and I/O devices. The memory and registers of the I/O devices are mapped to (associated with) address values. So when an address is accessed by the CPU, it may refer to a portion of physical RAM, but it can also refer to memory of the I/O device. Thus, the **CPU instructions used to access the memory can also be used for accessing devices**.

In this type of I/O interfacing, the 8086 uses 20 address lines to identify an I/O device. The I/O device is connected as if it is a memory device. The 8086 uses same control signals and instructions to access I/O as those of memory, here RD and WR signals are activated indicating memory bus cycle.

#### Problem :

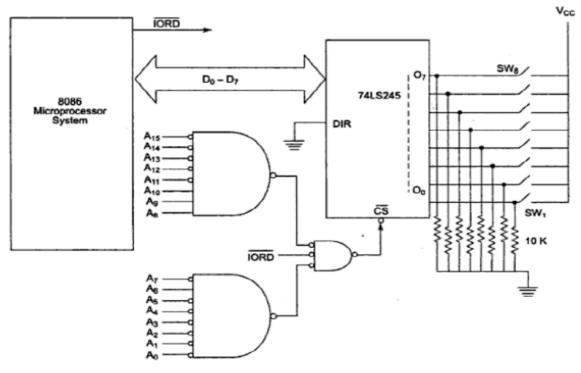

Interface an input port 74LS245 to read the status of the switches SW1 to SW8. the switches when shorted, input a '1' else input a '0' to the microprocessor system. Store the status in register BL. The address of the port is 0740H

Fig. Interfacing Input Port 74LS245

#### Solution :

The hardware interface circuit is shown in figure. The address, control and data lines are assumed to be readily available at the microprocessor system The ALP is given as follows

MOV BL, 00H ; clear BL for status MOV DX, 0740H ; 16-bit Port address in DX IN AL,DX ; Read Port 0740H for switch positions. MOV BL,AL ; Store status of switches from AL into BL HLT ; Stop

#### Problem :

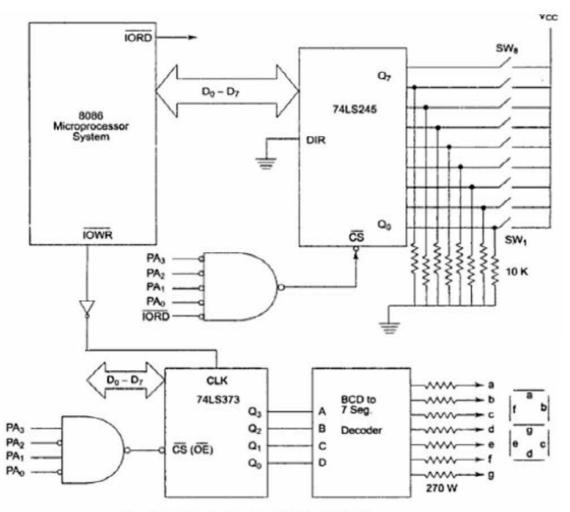

Design an interface of input port 74LS245 to read the status of switches SW1 to SW8 and output port 74LS373 with 8086. display the number of key that is pressed with the help of output port on 7 segment display.Write an assembly language program for this task.Assume that only one key is pressed at a time. Draw the schematic of the required

hardware. The imput port address is 0008H and the output port address is 000AH?

Solution : Since using all the address lines A0-A15 require lot of hardware, one may use only A0-A3 .Thus athe address 0008H can be converted into XXX8H where X denotes don't care condition.Thus the port may have more than one address for example 2358H, 1728 etc.

Only the LSB of the address need to be 8H.**Disadvantage** of this system is that, there are a number of addresses of the same port.Hence the system must have only one port that has the lowest nibble address 8H, otherwise the system may malfunction.Thus, for smaller systems containing a few I/O ports, this scheme is suitable. **Advantage** is it require less hardware.

Status of the switches is first read into the AL. Displaying the shorted switch number in the 7 segment display. Instead of using 16 address lines, one may use only A3– A0.

Fig. Interfacing Switches and Displays for Problem

Assembly language program is given below:

. .

. .

# Programmable input output port-8255

# Q.Explain input output operations of mode1?

# Q.Explain the internal architecture of 8255?

- The parallel input-output port chip 8255 is also called as programmable *peripheral input-output port*.

- *The Intel's* 8255 is designed for use with Intel's 8-bit, 16-bit and higher capability microprocessors.

- It has **24 input/output** lines which may be individually programmed in two groups of twelve lines each, or three groups of eight lines.

- The two groups of I/O pins are named as Group A and Group B.

- Each of these two groups contains a subgroup of eight I/O lines called as 8-bit port and another subgroup of four lines or a 4-bit port.

- Thus **Group A** contains an 8-bit port A along with a 4-bit port. C upper. **The port A** lines are identified by symbols PA0-PA7 .While the port C lines are identified as PC4-PC7.

- Similarly, **Group B** contains an 8-bit port B, containing lines PB0-PB7 and a 4-bit port C with lower bits PC0- PC3.

- The port C upper and port C lower can be used in combination as an 8-bit port C.

- All of these ports can function independently either as input or as output ports. This can be achieved by programming the bits of an internal register of 8255 called as control word register ( CWR ).

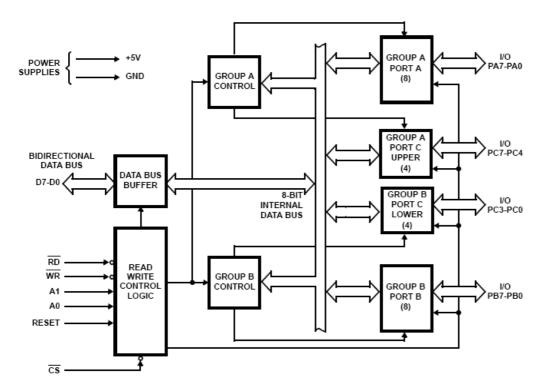

#### 8255 internal Architecture

8255 has a 40 pins of 4 groups.

- 1. Data bus buffer

- 2. Read Write control logic

- 3. Group A and Group B controls

- 4. Port A, B and C

- **Data bus buffer:** This is a tristate bidirectional buffer used to interface the 8255 to system databus. Data is transmitted or received by the buffer on execution of input or output instruction by the CPU. **Control word and status information** are also transferred through this unit.

- *Read/Write control logic:* This unit accepts control signals (RD, WR) and also inputs from address bus and issues commands to individual group of control blocks(Group A, Group B).

It has the following pins.

a)  $\overline{CS}$  – Chipselect : A low on this PIN enables the communication between CPU and 8255.

**b) RD** (**Read**) – A low on this pin enables the CPU to read the data in the ports or the status word through data bus buffer. \_\_\_\_\_

$c)\overline{WR}$  (Write): A low on this pin, the CPU can write data on to the ports or on to the control register through the data bus buffer.

**d**) **RESET:** A high on this pin clears the control register and all ports are set to the input mode

e) A0 and A1 ( Address pins ): These pins in conjunction with RD and WR pins control the selection of one of the 3 ports.

- *Group A and Group B controls : These block receive* control from the CPU and issues commands to their respective ports.

- Group A PA and PCU (PC7 –PC4)

- Group B –PB and PCL (PC3 PC0)

- **Control word register** can only be written into, no read operation of the CW register is allowed.

#### • PORT A,PORT B and PORT C

The 8255 contains three 8-bit ports (A, B, and C). All can be configured to a wide variety of functional characteristics by the system software but each has its own special features or "personality" to further enhance the power and flexibility of the 8255.

a) **Port A:** This has an 8 bit latched/buffered O/P and 8 bit input latch. It can be programmed in 3 modes – **mode 0,mode 1, mode 2.**

b) **Port B:** This has an 8 bit latched / buffered O/P and 8 bit input latch. It can be programmed in **mode 0, mode1**.

c) **Port C :** This has an 8 bit latched input buffer and 8 bit output latched/buffer. This port can be divided into two 4 bit ports and can be used as control signals for port A and port B. it can be programmed in **mode 0**.

# Pin Diagram-8255/ The signal description of 8255

# Q.Draw the signal descriptions of 8255?

Figure below shows the pin diagram of 8255:

| PA3             | 1  |      | 40 | PA4   |

|-----------------|----|------|----|-------|

| PA2             | 2  |      | 39 | PA5   |

| PA1             | 3  |      | 38 | PA6   |

| PA0             | 4  |      | 37 | PA7   |

| $\overline{RD}$ | 5  |      | 36 | WR    |

| ĈŜ              | 6  |      | 35 | RESET |

| gnd             | 7  |      | 34 | DO    |

| A1              | 8  |      | 33 | D1    |

| AD              | 9  |      | 32 | D2    |

| PC7             | 10 | 8255 | 31 | D3    |

| PC6             | 11 | PPI  | 30 | D4    |

| PC5             | 12 |      | 29 | D5    |

| PC4             | 13 |      | 28 | D6    |

| PC0             | 14 |      | 27 | D7    |

| PC1             | 15 |      | 26 | Vcc   |

| PC2             | 16 |      | 25 | PB7   |

| PC3             | 17 |      | 24 | PB6   |

| PB0             | 18 |      | 23 | PB5   |

| PB1             | 19 |      | 22 | PB4   |

| PB2             | 20 |      | 21 | PB3   |

|                 |    |      |    |       |

- The signal description of 8255 are briefly presented as follows :

- Total 40 pins are there:

- **PA7-PA0:** These are eight port A lines that acts as either latched output or buffered input lines depending upon the control word loaded into the control word register.

- **PC7-PC4 : Upper nibble of port C lines.** They may act as either output latches or input buffers lines. This port also can be **used for generation of handshake** lines in mode 1 or mode 2

- **PC3-PC0 : These are the lower port C lines, other details** are the same as PC7-PC4 lines.

- **PB0-PB7 : These are the eight port B lines which are used** as latched output lines or buffered input lines in the same way as port A.

- **RD** : This is the input line driven by the microprocessor and should be low to indicate read operation to 8255.

- WR : This is an input line driven by the microprocessor. Alow on this line indicates write operation.

- **CS** : This is a chip select line. If this line goes low, it enables the 8255 to respond to RD and WR signals, otherwise RD and WR signal are neglected.

- **A1-A0 :** These are the address input lines and are driven by the microprocessor. These lines A1-A0 with RD, WR and CS form the following operations for 8255.

- These address lines are used for addressing any one of the four registers, i.e. three ports and a control word register as given in table below:-

| [ <u> </u> |             |     | ٨                | ٨                | Input (Read) cycle   |

|------------|-------------|-----|------------------|------------------|----------------------|

| RD         | WR          | CS  | A <sub>1</sub>   | A <sub>0</sub>   | • • • •              |

| 0          | 1           | 0   | 0                | 0                | Port A to Data bus   |

| 0          | 1           | 0   | 0                | 1                | Port B to Data bus   |

| 0          | 1           | 0   | 1                | 0                | Port C to Data bus   |

| 0          | 1           | 0   | 1                | 1                | CWR to Data bus      |

|            |             |     |                  | Sec. 1           |                      |

| RD         | WR          | CS  | $\mathbf{A}_{1}$ | $\mathbf{A}_{0}$ | Output (Write) cycle |

| 1          | 0           | 0   | 0                | 0                | Data bus to Port A   |

| 1          | 0           | 0   | 0                | 1                | Data bus to Port B   |

| 1          | 0           | 0   | 1                | 0                | Data bus to Port C   |

| 1          | 0           | 0   | 1                | 1                | Data bus to CWR      |

| A A        |             |     | S Helfel         | 12               | Here and the here    |

| RD         | WR          | CS  | $\mathbf{A}_{1}$ | $\mathbf{A}_{0}$ | Function             |

| X          | Х           | 1   | Х                | Х                | Data bus tristated   |

| 1          | 1           | 0   | х                | Х                | Data bus tristated   |

| -121       | 1. 1. 1. A. |     | 1 (1) (1) (1)    |                  |                      |

|            |             | Con | trol Wor         | d Registe        |                      |

#### **Control Word Register**

• In case of 8086 systems, if the 8255 is to be interfaced with lower order data bus, the **A0 and A1 pins of 8255** are connected with **A1 and A2** respectively.

# **Modes of Operation of 8255**

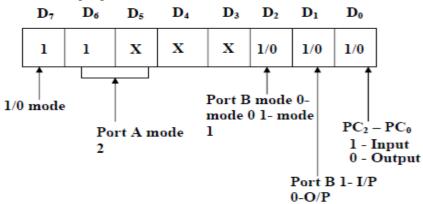

# Q.Specify the control word format of 8255?

# Q.Explain the modes of operations of 8255?

# Q.Describe the features of BSR mode?

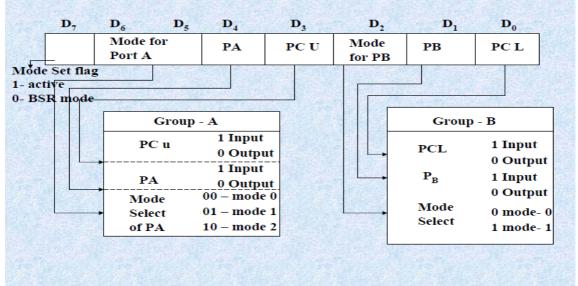

- These are two basic modes of operation of 8255.

- 1. .I/O mode

- 2. Bit Set-Reset mode (BSR).

- In I/O mode, the 8255 ports work as programmable I/Oports, while in BSR mode only port C (PC0-PC7) can be used to set or reset its individual port bits.

- Under the **I/O mode of operation**, further there are **three modes of operation of 8255**, so as to support differenttypes of applications, **mode 0**, **mode 1 and mode 2**.

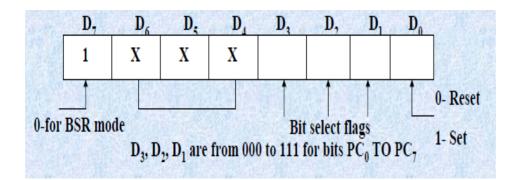

- **BSR Mode:** In this mode any of the 8-bits of port C can be set or reset depending on D0 of the control word. The bit to be set or reset is selected by bit select flags D3, D2 and D1 of the CWR as given in table.

| D <sub>3</sub> | D <sub>2</sub>                                       | D <sub>1</sub> | Selected bits of port C |  |  |  |  |  |  |  |  |

|----------------|------------------------------------------------------|----------------|-------------------------|--|--|--|--|--|--|--|--|

| 0              | 0                                                    | 0              | D <sub>0</sub>          |  |  |  |  |  |  |  |  |

| 0              | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |                |                         |  |  |  |  |  |  |  |  |

| 0              | 1                                                    | 1              | $\mathbf{D}_{3}^{2}$    |  |  |  |  |  |  |  |  |

| 1              | 0                                                    | 0              | D <sub>4</sub><br>D-    |  |  |  |  |  |  |  |  |

| 1              | 1                                                    | 0              | $D_5$<br>$D_6$          |  |  |  |  |  |  |  |  |

| 1              | 1                                                    | 1              | $\mathbf{D}_7$          |  |  |  |  |  |  |  |  |

|                |                                                      |                |                         |  |  |  |  |  |  |  |  |

|                | BSR M                                                | ode : CWR      | Format                  |  |  |  |  |  |  |  |  |

BSR control word register format is shown below:-

#### I/O Modes :

a) <u>Mode 0 (Basic I/O mode ):</u> This mode is also called as basic input/output mode. This mode provides simple input and output capabilities using each of the three ports. Data can be simply read from and written to the input and output ports respectively, after appropriate initialisation.

The salient features of this mode are as listed below:

1. Two 8-bit ports ( port A and port B )and two 4-bit ports (port C upper and lower ) are available. The two 4-bit ports can be combinedly used as a third 8-bit port.

2. Any port can be used as an input or output port.

3. Output ports are latched. Input ports are not latched.

4. A maximum of four ports are available so that overall 16 I/O configuration are possible.

• All these modes can be selected by programming a register internal to **8255 known** as **CWR**.

Control word format of 8255 is shown below:-

Now let us consider some interfacing problems so as to elaborate the hardware interfacing and I/O programming Ideas using 8255 in mode 0.

#### Problem.1

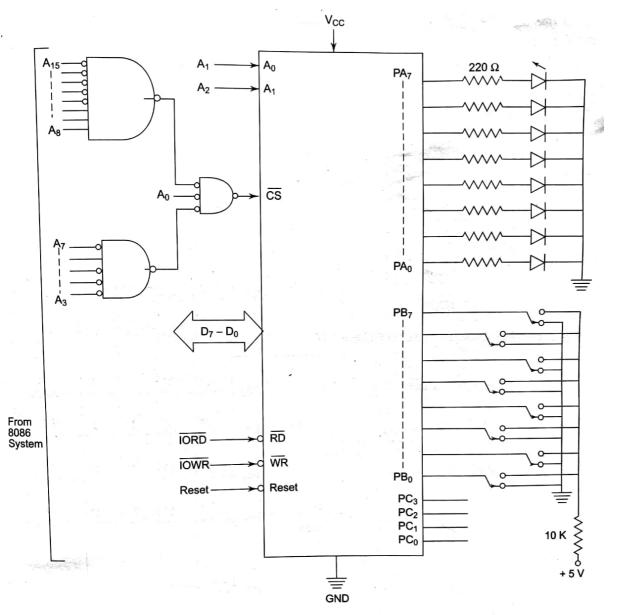

Interface an 8255 with 8086 to work as an I/O port. Initialize port A as output port, port B as input port and port C as output port. Port Å address should be 0740H. Write a program to sense switch positions  $SW_0$ -SW<sub>7</sub> connected at port B. The sensed pattern is to be displayed on port A, to which 8 LEDs are connected, while the port C lower displays number of on switches out of the total eight switches.

| Solution | The contro     | ol word is     | decided u      | pon as fo      | llows:         |                |       | and the standard                      |

|----------|----------------|----------------|----------------|----------------|----------------|----------------|-------|---------------------------------------|

| B7       | B <sub>6</sub> | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | Bo    | Control word                          |

| 1        | 0              | 0              | 0              | 0              | 0              | 1              | 0     | = 82H                                 |

| I/O      | Port A         | Address of the | Port           | Port           | Port           | Port           | Port  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| mode     | in mode 0      |                | A,o/p          | C,o/p          | B,mode 0       | B,i/p          | C,o/p |                                       |

Thus 82H is the control word for the requirements in the problem. The port address decoding can be done as given below. The 8255 is to be interfaced with lower order data bus, i.e.  $D_0$ - $D_7$ . The  $A_0$  and  $A_1$  pins of 8255 are connected to  $A_{01}$  and  $A_{02}$  pins of the microprocessor respectively. The  $A_{00}$  pin of the microprocessor is used for selecting the transfer on the lower byte of the data bus. Hence any change in the status of  $A_{00}$  does not affect the port to be selected, rather  $A_{01}$  and  $A_{02}$  of the microprocessor decide the port to be selected as they are connected to  $A_0$  and  $A_1$  of 8255. The 8255 port addresses are tabulated as shown below.

| 8255   |                 |                 |                 |                 |                 |                 |      | O Addr          |      |      |      |                 |                 | ~               | ~               | 4   | Hex. Port |

|--------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------|-----------------|------|------|------|-----------------|-----------------|-----------------|-----------------|-----|-----------|

| Ports  | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> | A <sub>10</sub> | A 09 | A <sub>08</sub> | A 07 | A 06 | A 05 | A <sub>04</sub> | A <sub>03</sub> | A <sub>02</sub> | A <sub>01</sub> | A00 | Addresses |

| PortA  | 0               | 0               | 0               | 0               | 0               | 1               | - 1  | 1               | 0    | 1    | 0    | 0               | 0               | 0               | 0               | 0   | 0740H     |

|        |                 |                 |                 |                 |                 | 1997<br>1997    |      |                 |      |      |      |                 |                 |                 |                 |     |           |

| Port B | 0               | 0               | 0               | 0               | 0               | 1               | 1    | 1               | 0    | 1    | 0    | 0               | 0               | 0               | 1               | 0   | 0742H     |

| 8255   | Sec. States                     |                 | New Street      | en an an an                     | I/(             | O Addr          | ess lin         | ies             |                 | 1               |                 |                 |                 | 120             | Hex. Port |

|--------|---------------------------------|-----------------|-----------------|---------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------|

| Ports  | A <sub>15</sub> A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> A <sub>10</sub> | A <sub>09</sub> | A <sub>08</sub> | A <sub>07</sub> | A <sub>06</sub> | A <sub>05</sub> | A <sub>04</sub> | A <sub>03</sub> | A <sub>02</sub> | A <sub>01</sub> | A <sub>00</sub> | Addresses |

| Port C | 0 0                             | 0               | 0               | 0 1                             | -1              | 1               | 0               | 1               | 0               | 0               | 0               | -1              | 0               | 0               | 0744H     |

| CWR    | 0 0                             | 0               | 0               | 0 1                             | 1               | 1               | 0               | 1               | 0               | 0               | 0               | 1               | 1               | 0               | 0746H     |

Let us use absolute decoding scheme that uses all the 16 address lines for deriving the device address pulse Out of  $A_0 - A_{15}$  lines, two address lines  $A_{02}$  and  $A_{01}$  are directly required by 8255 for the three port and CWR address decoding. Hence only  $\overline{A_3}$  to  $\overline{A_{15}}$  are used for decoding addresses. The complete hardware scheme is shown in Fig. 5.19. In the diagram, the 8086 is assumed to be in the maximum mode so that IORD and IOWR are readily available. If the 8086 is in minimum mode,  $\overline{RD}$  and  $\overline{WR}$  of 8086 are to be connected accordingly to 8255 and M/IO pin is combined with the chip select of above hardware suitably so as to select the 8255 when M/IO is low.

The ALP for the problem is developed as follows:

| MOV DX, 0746 H<br>MOV AL, 82 H<br>OUT DX, AL                                                                                                         | ; Initialise CWR with<br>; control word 82H<br>; get colder of post &                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SUB DX,04<br>IN AL, DX<br>SUB DX,02                                                                                                                  | ; Get address of port B in DX<br>; Read port B for switch<br>; positions in to AL and get port A address<br>in DX                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| OUT DX, AL<br>MOV BL, 00 H<br>MOV CH, 08H<br>YY: ROL AL<br>JNC XX<br>INC BL<br>XX : DEC CH<br>JNZ YY<br>MOV AL, BL<br>ADD DX, 04<br>OUT DX,AL<br>HLT | <ul> <li>j Display switch positions on port A</li> <li>j Display switch positions on port A</li> <li>j Initialise BL for switch count</li> <li>j Initialise BL for switch count</li> <li>j Initialise CH for total switch number</li> <li>k Rotate AL through carry to check,</li> <li>j whether the switches are on or</li> <li>j off, i.e. either 1 or 0</li> <li>j Check for next switch. If</li> <li>j all switch are checked, the</li> <li>j number of on switches are</li> <li>j in BL.Display it on port C</li> <li>j lower.</li> <li>j Stop</li> </ul> |  |

Program 5.5 ALP for Problem 5.10

Fig. 5.19 8255 Interfacing with 8086 for Problem 5.10

#### Problem 2:

#### Problem 5.11

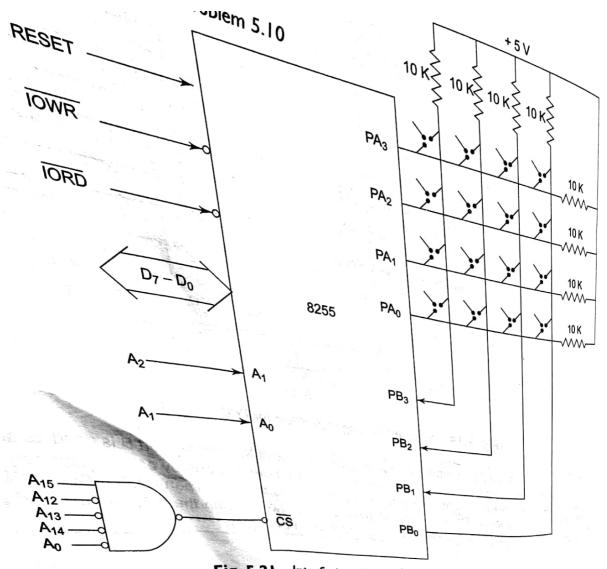

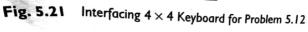

Interface a 4\*4 Keyboard with 8086 using 8255. and write an ALP for detecting a key closure and return the key code in AL. The debouncing period for a key is 10 ms. Use software key debouncing technique. DEBOUNCE is an available 10 ms delay routine.

Solution Port A is used as output port for selecting a row of keys while port B is used as an input port for sensing a closed key. Thus the keyboard lines are selected one by one through port A and the port B lines are polled continuously till a key closure is sensed. Then routine DEBOUNCE is called for key debouncing. The key code is decided depending upon the selected row and a low sensed column. The hardware circuit diagram is shown in Fig. 5.21.

The higher order lines of port A and port B are left unused. The addresses of port A and port B will be respectively 8000 H and 8002 H while the address of CWR will be 8006 H. The flow chart of the complete program is given in Fig. 5.22.

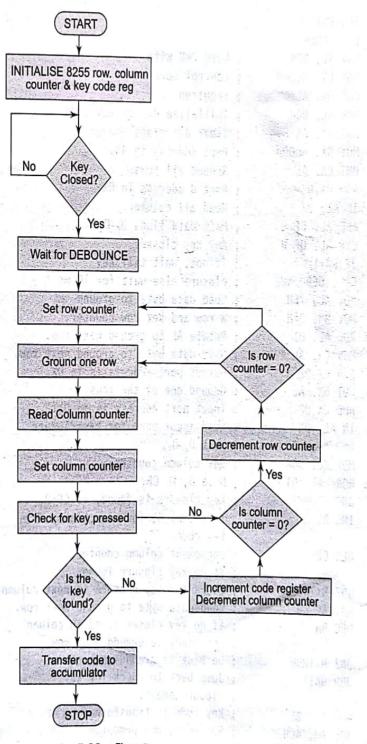

Fig. 5.22 Flow Chart for ALP of Problem 5.11

The ALP for the problem is given along with comments. The control word for this problem will be 82 H. Let us write this program using assembler directives. In this problem no major data is required

hence only one segment is used for storing the program code, i.e. code segment (CS). This program is written in MASM syntax. The 8255 is again interfaced to the lower byte of the 8086 data bus. Absolute decoding scheme is not used here to implement the circuit using minimum hardware.

| CODE     | SEGM | ENT       |   |                                                              |         |

|----------|------|-----------|---|--------------------------------------------------------------|---------|

| ASSUME   | CS : | CODE      |   |                                                              |         |

| START:   |      | AL, 82H   | ÷ | Load CWR with                                                |         |

| •        |      | DX, 8006H |   | control word                                                 |         |

|          |      | DX, AL    |   | required                                                     |         |

|          |      | BL, 00H   |   | Initialize BL for key code                                   |         |

|          |      | AX, AX    |   | Clear all flags                                              |         |

|          |      | DX, 8000H |   | Port Address in AX.                                          |         |

|          |      | DX, AL    | - | Ground all rows.                                             |         |

|          |      | DX,02     |   | Port B address in DX.                                        |         |

| WAIT :   |      | _, DX     |   | Read all columns.                                            |         |

|          |      | AL, OF H  |   | Mask data lines $D_7 - D_4$ .                                | OF ->15 |

|          |      | AL, OF H  |   | Any key closed?                                              |         |

| 122      | JZ W |           |   | If not, wait till key                                        |         |

|          |      | DEBOUNCE  |   | closure else wait for 10 ms                                  |         |

|          |      | AL, 7FH   |   | Load data byte to ground                                     |         |

|          |      | BH, 04H   |   | a row and set row counter.                                   |         |

| NXTROW : |      |           |   | Rotate AL to ground next row.                                |         |

|          |      | CH, AL    |   | Save data byte to ground next row.                           |         |

|          |      | DX,02     |   | Output port address is in DX.                                |         |

|          |      | DX, AL    |   | Ground one of the rows.                                      |         |

|          |      | DX,02     |   | Input port address is in DX.                                 |         |

|          |      | L, DX     |   | Read input port for key closure.                             |         |

|          |      | AL, OFH   |   | Mask $D_4 - D_7$ .                                           |         |

|          |      | CL, 04H   |   | Set column counter.                                          |         |

| NXTCOL : | ROR  | AL, 01    | ; | Move $D_0$ in CF.                                            |         |

|          |      | CODEKY    |   | Key closure is found, if CF=0.                               |         |

|          | INC  | BL        | ; | Increment BL for next binary                                 |         |

|          |      |           |   | key code.                                                    |         |

|          | DEC  | CL        |   | Decrement column counter,                                    |         |

|          |      | -         |   | if no key closure found.                                     |         |

|          |      | NXTCOL    |   | Check for key closure in next column                         |         |

|          | DEC  | AL,CH     |   | Load data byte to ground next row.                           |         |

|          | DLC  | ы         |   | if no key closer found in column                             |         |

| Sec. and | JNZ  | NXTROW    |   | get ready to ground next row.<br>Go back to ground next row. |         |

|          |      | WAIT      |   | Jump back to check for key.                                  |         |

|          |      |           |   | closure again.                                               |         |

| CODEKY   |      | AL, BL    |   | Key code is transferred to AL.                               |         |

|          |      | AH, 4CH   |   | Return to DOS prompt.                                        |         |

| 1        | INT  | 21 H      |   |                                                              |         |

|          |      |           |   |                                                              |         |

0000 111

This procedure generates 10 ms delay at 5 MHz operating frequency.

Contraction and the second

| DEBOUNCE      | PROC | NEAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | MOV  | CL, OE2H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BACK:         | NOP  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| un an an an a | DEC  | CL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               | JNZ  | BACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | RET  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DEBOUNCE      | END  | $\mathbf{P}^{i}$ . We have the first second secon |

| CODE          | END  | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               | FND  | START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# Problem.1

Interface an 8255 with 8086 to work as an I/O port. Initialize port A as output port, port B as input port and port C as output port. Port A address should be 0740H. Write a program to sense switch positions  $SW_0-SW_7$  connected at port B. The sensed pattern is to be displayed on port A, to which 8 LEDs are connected, while the port C lower displays number of on switches out of the total eight switches.

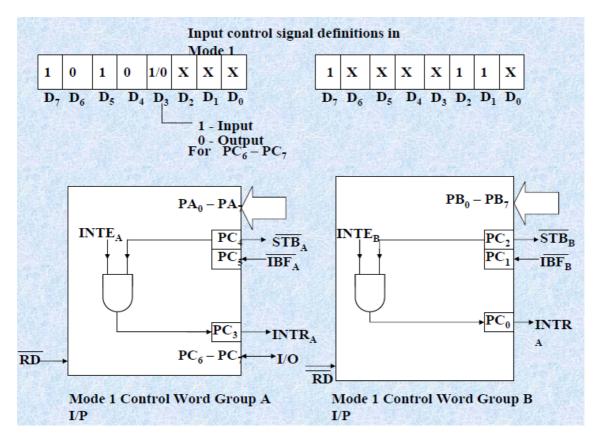

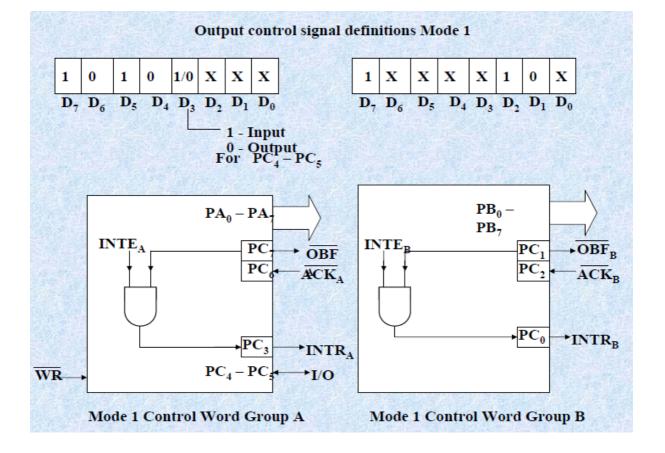

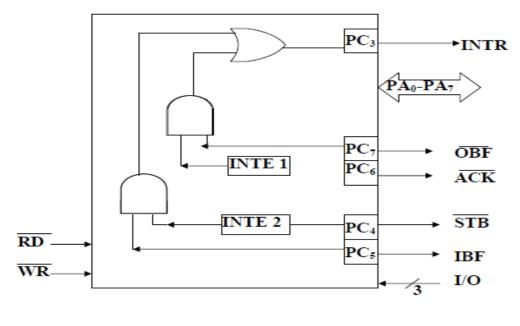

# a) Mode 1: ( Strobed input/output mode )

- *In this mode the* handshaking signals control the input and output action of the specified port.

- Port C lines PC0-PC2, provide strobe or handshake lines for port B. This group which includes port B and PC0-PC2 is called as group B for Strobed data input/output.

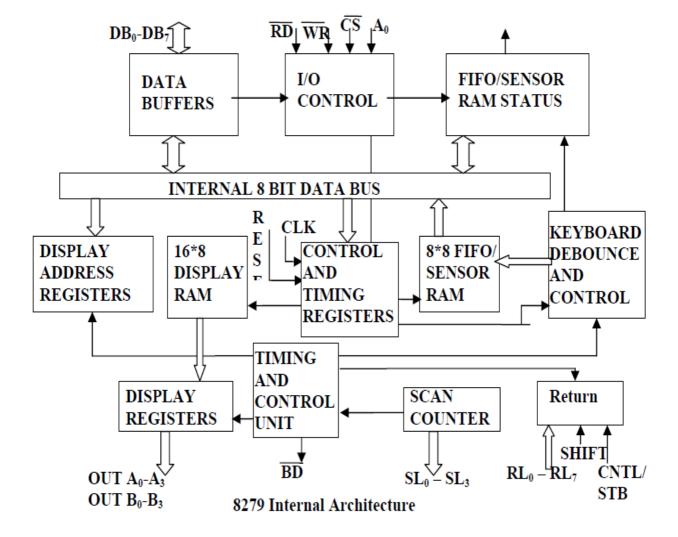

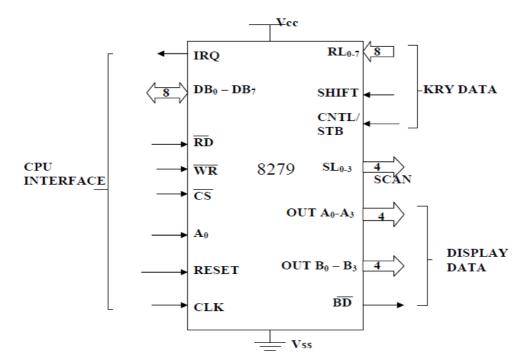

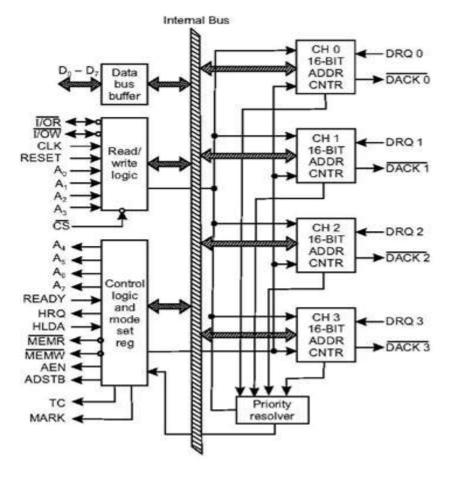

- Port C lines PC3-PC5 provide strobe lines for port A. This group including port A and PC3-PC5 from group A. Thus port C is utilized for generating handshake signals.